# ASSPおよびASICの代替となる FLEX デバイス

Technical Brief-3

1996年2月

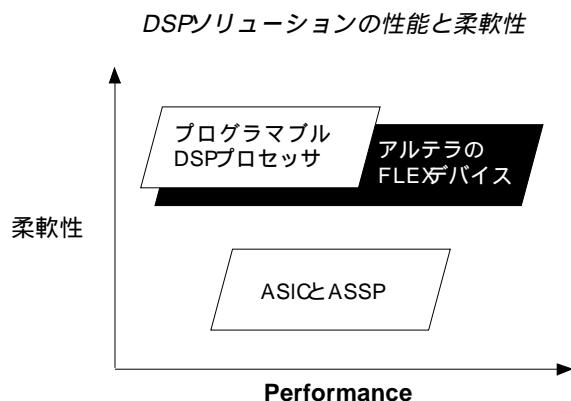

これまで、リアル・タイムの性能が要求されるディジタル信号処理（DSP）のアプリケーションには、ASSP（特定用途向けの標準IC）やASICが使用されていました。これらのソリューションは使用可能なレベルの性能は提供しますが、DSPのアルゴリズムの一部を変更できるような高い柔軟性を提供することはできません。アルテラのFLEX 8000とFLEX 10Kのプログラマブル・ロジック・デバイス（PLD）ファミリは、ASSPやASICデバイスで実現したときと同じような性能をさらに低コストで実現し、同時にさらに高い柔軟性も提供します。

## FLEX DSPの利点

FLEXデバイスを使用することによって、性能を犠牲にすることなく、短時間で試作を完成させ、また設計変更を簡単に行うことができます。例えば、EPF8452Aで実現された8タップのFIR（Finite Impulse Response）フィルタは、100MSPS（Million Samples Per Second）のスピードで動作することができます。FLEXデバイスはリコンフィギュラブルとなっているため、目的のファンクションの実現方法を変更することができます。これまでプロセッサのインストラクションのシーケンスで実現されていたアルゴリズムをFLEXデバイスの内部にパラレルに実現することも可能です。

## 効率

FIRフィルタやYUV-RGB変換などのように、DSPで使用される多くのアルゴリズムには、係数との乗算が必要になります。ルック・アップ・テーブル（LUT）をベースにしたFLEXアーキテクチャでは、被定数に相当するベクタをあらかじめ計算してLUTにストアしておくことができるため、完全な乗算器を構成する必要がありません。ASICなどのようにリコンフィギュラブルとなっていないデバイスでは、同じファンクションを実現する場合にフル構成の乗算器が必要になります。

## パイプライン化

ASICやASSPにおいて、パフォーマンスの改善のためにパイプライン・レジスタが使用されると、必要なロジック・リソースが増加します。これに対して、FLEX 8000とFLEX 10Kデバイスの各ロジック・セルにはレジスタが内蔵されているため、追加のロジック・リソースを使用することなく、これらのレジスタをパイプライン・レジスタとして使用することができます。

## イン・サーキット・リコンフィギュラビリティ（ICR）

ICRの機能を活用することによって、システムの通常の動作中にFLEXデバイスをリコンフィギュレーションすることができます。また、ICRの機能を使って、ボード上に実装されたデバイスが外部から自動的にリコンフィギュレーションされるようにし、同一のロジック・リソースで複数の機能を実現することも可能です。また、ICRの機能を活用して、フィールドに設置されたシステムの内部動作アルゴリズムをアップデートすることも可能です。

## 特殊なアルゴリズム

FLEX 10Kのエンベデッド・アレイ・ブロックには、高速フーリエ変換(FFT)や離散コサイン変換(DCT)などのように、演算の中間値をストアし、これを高速で何回も繰り返して使用することが要求される特殊なアルゴリズムを実現することができます。

## FLEX DSPの性能

その高い効率と高速で遅延の予測が可能な配線リソースとなっているFast Trackにより、FLEXデバイスは、各DSPファンクションをASICやASSPよりもはるかに高いコスト・パフォーマンスで実現します。下記の表は $3 \times 3$ のビデオ・コンポルバをアルテラのEPF8452Aで実現したときの性能と価格を、同じファンクションをハリスのASSP ICであるHSP48901、および50MHzの固定少数点DSPプロセッサで実現した場合と比較したものです。

### $3 \times 3$ ビデオ・コンポルバの性能比較

| ソリューション          | 使用デバイス           | 性能(MSPS) | 相対価格 |

|------------------|------------------|----------|------|

| FLEX 8000        | アルテラ EPF8452A    | 98       | 1.0  |

| ビルディング・ブロックのASSP | ハリス HSP48901     | 30       | 3.0  |

| DSPプロセッサ         | T.I TMS320325-50 | < 2      | 2.8  |

ASSPの専用回路では、フル構成の乗算器を実現する必要があるため、結果的にFLEXデバイスよりも性能が66%も低くなっています。また、標準的なDSPプロセッサでは、9回の実行が必要な乗算累積演算(MAC)が各クロック・サイクルごとに1回ずつしか実行できず、データのリードにも追加の時間が必要になります。このため、DSPプロセッサの性能はFLEXデバイスよりも大幅に低下してしまいます。さらに、ASSPとDSPプロセッサによるソリューションはFLEXデバイスの場合よりも高価になります。

## アルテラのDSPデザイン・キット

FLEXデバイスは、柔軟性を犠牲にすることなく、カスタムのDSPソリューションよりも高い性能を提供します。アルテラはDSPデザイン・キットを提供しています。このDSPデザイン・キットには、各種のDSPファンクションが実現できるカスタマイズ可能なビルディング・ブロックが含まれています。これらのビルディング・ブロックには、データと係数の幅がカスタマイズ可能なフル・パラレル構成の8、16、24、32、64タップのFIRフィルタ、タップ数の大きなフィルタが構成できるフル・シリアル構成のフィルタ、浮動小数点演算機能などが含まれています。DSPデザイン・キットで提供されているこれらのファンクションは、アルテラのFLEXアーキテクチャに最適化されており、各デザインで要求されるパラメータに応じてこれらのファンクションをカスタマイズすることができます。

---

さらに詳しい情報が下記の資料で提供されています。最後に表示されている記号は、各資料のドキュメント番号です。

### プロダクト・インフォメーション・ブリティン

PIB 23 Digital Signal Processing in FLEX Devices(日本語版：FLEXデバイスによるディジタル信号処理) A-PIB-023-01

### アプリケーション・ノート

AN 73 Implementing FIR Filters in FLEX Devices(日本語版：FLEXデバイスによるFIRフィルタの実現) A-AN-073-01

これらの資料は、日本アルテラおよび各販売代理店にご請求下さい。また、英文の資料については、アルテラのWWWサイト、<http://www.altera.com>からダウンロードすることができます。

日本アルテラ株式会社 〒163-04 東京都新宿区西新宿2-1-1 新宿三井ビル内郵便局私書箱261号

TEL. 03-3340-9480 FAX. 03-3340-9487